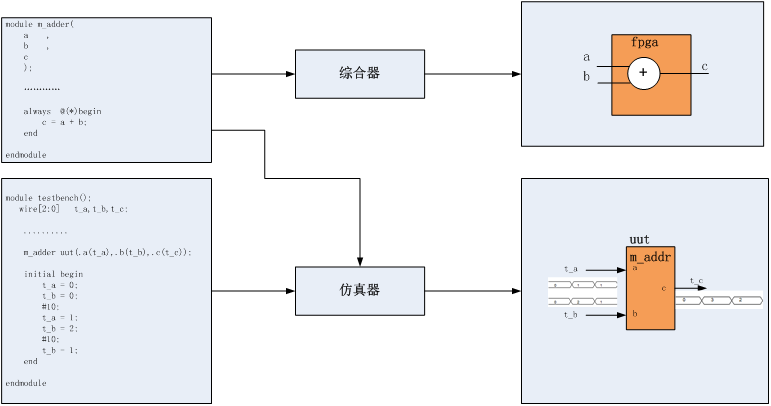

Verilg是硬件描述语言,顾名思义,就是用代码的形式描述硬件的功能。而我们最终是要在电路上实现该功能的。当Verilog描述出硬件功能后,我们需要综合器对Verilog代码进行解释,将代码转化成实际的电路来表示,最终实际的电路,我们称之为网表。这种将Verilog代码转成网表的工具,就是综合器。上图左上角是一份verilog代码,该代码描述了一个加法器功能。该代码经过综合器解释后,转化成一个加法器电路。QUARTUS、ISE和VIVADO都是综合器,集成电路常用的综合器是DC。

我们在FPGA设计的过程中,不可避免会出现各种BUG。如果我们编写好代码,综合成电路,烧写到FPGA后,才看到问题,此时去定位问题就会非常地困难了。在综合前,我们可以在电脑里对代码进行仿真测试一下,把BUG找出来解决,最后才烧写进FPGA。我们可以认为,没有经过仿真验证的代码,一定是存在BUG的。

为了模拟真实的情况,我们需要编写测试文件。该文件也是用verilog编写的,描述了仿真对象的输入激励情况。该激励力求模仿最真实的情况,产生最将近的激励信号,将该信号的波形输入给仿真对象,查看仿真对象的输出是否与预期一致。

为了做仿真验证,我们编写了测试文件。将测试文件和被测试对象加入到仿真器中。仿真器对测试文件和被测试对象的代码进行解释。根据测试文件,产生测试激励,输入给被测试对象;根据补测试对象的代码,产生被测试对象的输出。需要注意的是,在仿真过程中,没有将代码转成电路,仿真器只是对代码进行仿真验证。至于该电路是否可转成电路,仿真器是不关心的。

常用的仿真器是MODELSIM和VCS等。

由此可见,verilog的代码不仅可以描述电路,还可以用于测试。事实上,Verilog定义的语法非常之多,但绝大部分都是为了仿真测试来使用的。只有少部分才是用于电路设计,详细可以参考本书的“可综合逻辑设计”一节。

Verilog中用于设计的语法,才是学习的重点。掌握好设计的语法,熟练应用于各种复杂的项目,这是技能的核心。其他测试用的语法,需要时查找和参考就已经足够了。

本书着重点,是用于本科、研究生的教学用途,因此将重点讲解设计用的语法。

在本章讲解Verilg时,将从综合器和仿真器角度,解释语法的用途,读者可以明白要学习的关键内容。

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。